# Lecture Notes in Computer Science Edited by G. Goos, J. Hartmanis, and J. van Leeuwen

2648

Springer Berlin Heidelberg New York Barcelona Hong Kong London Milan **Paris** Tokyo

# Model Checking Software

10th International SPIN Workshop Portland, OR, USA, May 9-10, 2003 Proceedings

#### Series Editors

Gerhard Goos, Karlsruhe University, Germany Juris Hartmanis, Cornell University, NY, USA Jan van Leeuwen, Utrecht University, The Netherlands

Volume Editors

Thomas Ball Sriram K. Rajamani Microsoft Research One Microsoft Way, Redmond, WA 98052, USA E-mail: {tball, sriram}@microsoft.com

Cataloging-in-Publication Data applied for

A catalog record for this book is available from the Library of Congress

Bibliographic information published by Die Deutsche Bibliothek Die Deutsche Bibliothek lists this publication in the Deutsche Nationalbibliographie; detailed bibliographic data is available in the Internet at <a href="http://dnb.ddb.de">http://dnb.ddb.de</a>>.

CR Subject Classification (1998): F.3, D.2.4, D.3.1, D.2

ISSN 0302-9743 ISBN 3-540-40117-2 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

Springer-Verlag Berlin Heidelberg New York a member of BertelsmannSpringer Science+Business Media GmbH

http://www.springer.de

© Springer-Verlag Berlin Heidelberg 2003 Printed in Germany

Typesetting: Camera-ready by author, data conversion by DA-TeX Gerd Blumenstein Printed on acid-free paper SPIN: 10929896 06/3142 5 4 3 2 1 0

#### **Preface**

This volume contains the proceedings of SPIN 2003, the 10th International SPIN Workshop on Model Checking of Software. The workshop was held during May 9–10, 2003, in Portland, Oregon. The program committee of the workshop had the following members:

Thomas Ball (Microsoft Research)

Matthew Dwyer (Kansas State University)

Javier Esparza (University of Stuttgart)

Kousha Etessami (University of Edinburgh)

Patrice Godefroid (Bell Laboratories)

Susanne Graf (VERIMAG)

Somesh Jha (University of Wisconsin)

Peter O'Hearn (University of London)

Andreas Podelski (Max Planck Institute)

Sriram K. Rajamani (Microsoft Research)

Mooly Sagiv (Tel Aviv University)

Scott Stoller (State University of New York at Stony Brook)

The advisory committee for the SPIN workshops consisted of Gerard Holzmann (Chair) and Amir Pnueli. The steering committee for the SPIN workshops consisted of Matthew Dwyer, Stefan Leue, Moshe Vardi (Chair) and Pierre Wolper.

There is a renewed interest in building tools to improve the reliability of software by detecting errors early in the software development process. The SPIN model checker has played a leading role in this new research direction: it has been used in a new tool FeaVer for model checking concurrent software written in ANSI-C. Additionally, there are a variety of techniques for specifying descriptions of intended behavior (such as temporal logics and state machines) as well as techniques to perform the checking (such as model checking, compiler-style static analysis, type systems, theorem proving and run-time analysis). In view of these developments, SPIN 2003 took a broader view and addressed the general problem of specifying and checking properties of software systems. We organized a diverse workshop where people with backgrounds in different analysis areas met and presented different approaches and viewpoints about the general problem of specifying and checking properties of software.

Papers went through a rigorous reviewing process. Each paper was reviewed by three program committee members. Of 39 papers submitted, 14 regular papers and 3 tool papers were accepted.

In addition to the refereed papers, invited talks were given by Gerard Holzmann (Bell Laboratories) on *History of the SPIN Model Checker* and George Necula (University of California at Berkeley) on *Randomized Algorithms for Program Analysis and Verification*.

The program committee is grateful to the following reviewers for their help in evaluating the paper submissions: Luca de Alfaro, Josh Berdine, Dragan

#### VI Preface

Bošnački, Ahmed Bouajjani, Marius Bozga, Lubos Brim, Cristiano Calcagno, Tom Chothia, Craig A. Damon, Giorgio Delzanno, Juergen Dingel, Nurit Dor, Radu Grosu, Victor Khomenko, Sarfraz Khurshid, Barbara Koenig, Raghavan Komondoor, Gerard Holzmann, Michael Huth, Markus Lohrey, Alexey Loginov, Monika Maidl, Patrick Maier, Roman Manevich, Kedar Namjoshi, Stefan Schwoon, Ran Shaham, Perdita Stevens, Thomas Wilke, Farn Wang, Eran Yahav, and Marc Zeitoun.

We are grateful to the program committee, the reviewers, the invited speakers, the sponsors, the authors of the papers, and the attendees for making the workshop a success.

Redmond, May 2003

Thomas Ball Sriram K. Rajamani

# Table of Contents

| Optimal Scheduling Using Branch and Bound with SPIN 4.0                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------|

| A Requirements Patterns-Driven Approach<br>to Specify Systems and Check Properties                                                   |

| Formal Modeling and Analysis of an Avionics Triplex Sensor Voter34  Samar Dajani-Brown, Darren Cofer, Gary Hartmann, and Steve Pratt |

| Distributed Explicit Fair Cycle Detection (Set Based Approach)                                                                       |

| Efficient Model Checking of Safety Properties                                                                                        |

| A Light-Weight Algorithm for Model Checking with Symmetry Reduction and Weak Fairness                                                |

| A SAT Characterization of Boolean-Program Correctness                                                                                |

| What Went Wrong: Explaining Counterexamples                                                                                          |

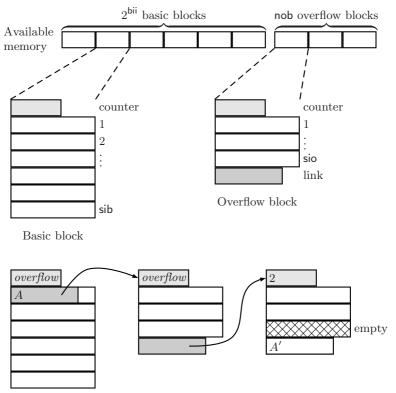

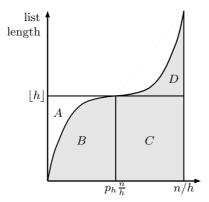

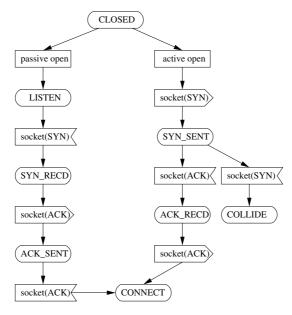

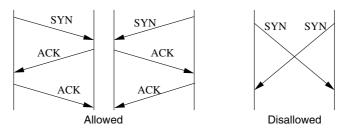

| A Nearly Memory-Optimal Data Structure for Sets and Mappings 136<br>Jaco Geldenhuys and Antti Valmari                                |

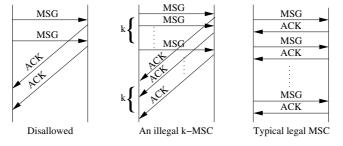

| Checking Consistency of SDL+MSC Specifications                                                                                       |

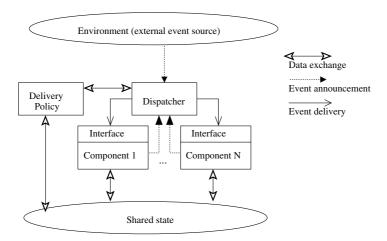

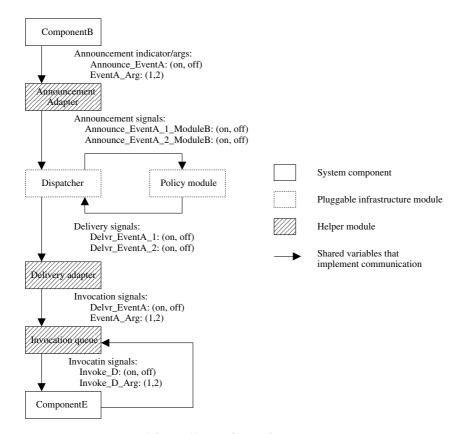

| Model Checking Publish-Subscribe Systems                                                                                             |

| A Methodology for Model-Checking Ad-hoc Networks                                                                                     |

| Promela Planning                                                                                                                     |

| Thread-Modular Model Checking                                                                                                        |

| Unification & Sharing in Timed Automata Verification                                                                                 |

| The Maude LTL Model Checker and Its Implementation                                                                                   |

#### VIII Table of Contents

| Software Verification with BLAST                   | 235 |

|----------------------------------------------------|-----|

| Thomas A. Henzinger, Ranjit Jhala, Rupak Majumdar, |     |

| and Grégoire Sutre                                 |     |

|                                                    |     |

| Author Index                                       | 241 |

# Optimal Scheduling Using Branch and Bound with SPIN 4.0

Theo C. Ruys\*

Department of Computer Science, University of Twente P.O. Box 217, 7500 AE Enschede, The Netherlands. ruys@cs.utwente.nl

http://www.cs.utwente.nl/~ruys/

Abstract. The use of model checkers to solve discrete optimisation problems is appealing. A model checker can first be used to verify that the model of the problem is correct. Subsequently, the same model can be used to find an optimal solution for the problem. This paper describes how to apply the new PROMELA primitives of SPIN 4.0 to search effectively for the optimal solution. We show how Branch-and-Bound techniques can be added to the LTL property that is used to find the solution. The LTL property is dynamically changed during the verification. We also show how the syntactical reordering of statements and/or processes in the PROMELA model can improve the search even further. The techniques are illustrated using two running examples: the Travelling Salesman Problem and a job-shop scheduling problem.

#### 1 Introduction

SPIN [10, 11, 12] is a model checker for the verification of distributed systems software. SPIN is freely distributed, and often described as one of the most widely used verification systems. During the last decade, SPIN has been successfully applied to trace logical design errors in distributed systems, such as operating systems, data communications protocols, switching systems, concurrent algorithms, railway signaling protocols, etc. [13]. This paper discusses how SPIN can be applied effectively to solve discrete optimisation problems.

Discrete optimisation problems are problems in which the decision variables assume discrete values from a specified set; when this set is set of integers, we have an integer programming problem. Combinatorial optimisation problems are problems of choosing the best combination out of all possible combinations. Most combinatorial problems can be formulated as integer programs.

In recent years, model checkers have been used to solve a number of non-trivial optimisation problems (esp. scheduling problems), reformulated in terms of reachability, i.e. as the (im)possibility to reach a state that improves on a given optimality criterion [2, 5, 7, 8, 15, 20]. Techniques from the field of operations

<sup>\*</sup> This work is partially supported by the European Community IST-2001-35304 Project AMETIST (Advanced Methods for Timed Systems).

T. Ball and S. K. Rajamani (Eds.): SPIN 2003, LNCS 2648, pp. 1-17, 2003.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2003

research [22] – e.g. Branch-and-Bound [3] techniques – are being applied to prune parts of the search tree that are guaranteed not to contain optimal solutions. Model checking algorithms have been extended with optimality criteria which provided a basis for the guided exploration of state spaces [2, 15].

Though SPIN has been used to solve optimisation problems (i.e. scheduling problems [5, 20]), the procedures used were not very efficient and the state space was not pruned in any way. This paper shows how the new version of SPIN can be used to effectively solve discrete optimisation problems, especially integer program problems. We show how Branch-and-Bound techniques can be added to both the PROMELA model and – even more effectively – to the property  $\phi$  that is being verified with SPIN. To improve efficiency we let the property  $\phi$  dynamically change during the verification. We also show how the PROMELA model can be reordered syntactically to guide the exploration of the state space. The paper does not compare existing techniques to solve optimisation problems to the one presented here; we only show how one might use vanilla SPIN to solve (small) optimisation problems.

The paper tries to retain the tutorial style of presentation of [18, 19] to make the techniques easy to adopt by intermediate SPIN users. The techniques are explained by means of running examples of two classes of optimisation problems. The effectiveness of the techniques is illustrated by some experiments.

The paper is structured as follows. In Section 2 we introduce the Travelling Salesman Problem (TSP) and show how SPIN can be used to find the optimal solution for this problem. Section 3 briefly describes the new primitives of SPIN 4.0. In section 4 we show how the new primitives can be used to solve a TSP more effectively. In section 5 we apply the same techniques to a job-shop scheduling problem and show how Branch-and-Bound techniques can elegantly be isolated in the property which is being verified. The paper is concluded in Section 6.

Experiments. All verification experiments for this paper were run on a Dell Inspiron 4100 Laptop computer driven by a Pentium III Mobile/1Ghz with 384Mb of main memory. All pan verification runs were limited to 256Mb though. The experiments were carried out under Windows 2000 Professional and Cygwin 1.3.6; the pan verifiers were compiled using gcc version 2.95.3-5. For our experiments we used SPIN version 4.0.1 (7 Jan 2003). To compile the pan verifiers, we used the following options for gcc:

```

GCC OPTIONS="-w -D POSIX SOURCE -DMEMLIM=256 -DSAFETY -DXUSAFE -DNOFAIR"

```

For Promela models without a never-claim, we added the -DNOCLAIM option. We executed the pan verifiers using the following directives:

```

PAN_OPTIONS="-m1000 -w20 -c1"

```

## 2 TSP with Plain Spin

The Traveling Salesman Problem (TSP) [16, 17] is a well known optimisation problem from the area of operations research [22]. In a TSP, n points (cities) are

|   | 0 | 1 | 2 | 3 |

|---|---|---|---|---|

| 0 | - | 7 | 9 | 2 |

| 1 | 4 | - | 3 | 7 |

| 2 | 6 | 7 | - | 8 |

| 3 | 2 | 3 | 8 | - |

|   |   |   |   |   |

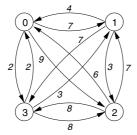

Fig. 1. Graph and matrix representation of the  $4 \times 4$  example TSP

given, and every pair of cities i and j is separated by a distance (or cost)  $c_{ij}$ . The problem is to connect the cities with the shortest closed tour, passing through each city exactly once. A specific TSP can be specified by a distance (or cost) matrix. An entry  $c_{ij}$  in row i and column j specifies the cost of travelling from city i to city j. The entries could be the Euclidean distances between cities in a plane, or simply costs – making the problem non-Euclidean. Extensive research has been devoted to heuristics for the Euclidean TSP (see e.g. [17]). Construction heuristics for the non-Euclidean TSP are much less investigated. This paper considers non-Euclidean TSPs only. The TSP is NP-complete.

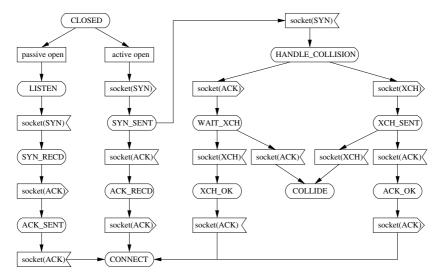

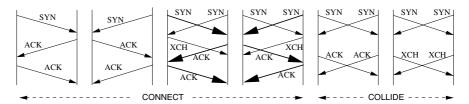

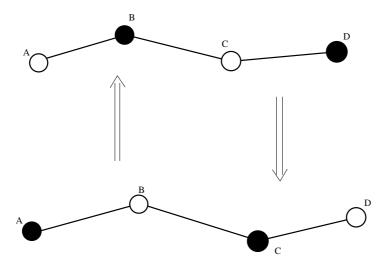

Modelling a TSP in PROMELA is straightforward. To illustrate the idea we develop a PROMELA model for the sample TSP of Fig. 1. Fig. 1 shows both a graph- and matrix-representation of a  $4 \times 4$  TSP. Fig. 2 shows the PROMELA model of the TSP of Fig. 1. The salesman itself is modelled by a single process TSP. For each place i that the man has to visit, there is a label Pi in the process TSP. The salesman starts at label P0. From each label Pi the salesman can (non-deterministically) go to any label Pj that has not been visited yet. A bit-array visited is used to keep track of the places that have already been visited. If, after reaching place Pi, it turns out that all places have been visited, the salesman has to go back to place P0. To keep track of the travelling costs, a variable cost is used. This variable is initialised on 0. When we move from place Pi to Pj, this variable is updated with the cost  $c_{ij}$  from the cost-matrix of Fig. 1.

Now that we have a PROMELA model of the TSP, we want to use SPIN to find the optimal route of the TSP. Fig. 3 shows a general algorithm for finding an optimal solution for an optimisation problem using a model checker. The procedure has been used in [5, 20]. The algorithm iteratively verifies whether 'the cost will eventually be greater than min'. Each time this property is violated, SPIN has found a path leading to a final state for which the cost is less than min. For each error, SPIN generates an error trail which corresponds with the better route. As the number of possible routes is finite, at a certain point SPIN will not find a route for which the cost is less than the min found so far. Consequently,

<sup>&</sup>lt;sup>1</sup> In this example we use Promela's built-in support for bit-arrays. In our experiments, however, we used the bit-vector library as discussed in [18], which are more efficient.

```

bit visited[3];

int cost:

active proctype TSP()

PO: atomic {

if

:: !visited[1] -> cost = cost + 7 ; goto P1

:: !visited[2] -> cost = cost + 9 ; goto P2

:: !visited[3] -> cost = cost + 2 ; goto P3

}

P1: atomic {

visited[1] = 1;

if

:: !visited[2] -> cost = cost + 3 ; goto P2

:: !visited[3] -> cost = cost + 7 ; goto P3

-> cost = cost + 4 ; goto end

fi;

P2: atomic {

visited[2] = 1;

if

:: !visited[1] -> cost = cost + 7 ; goto P1

:: !visited[3] -> cost = cost + 8 ; goto P3

-> cost = cost + 6 ; goto end

:: else

fi:

}

P3: atomic {

visited[3] = 1;

!visited[1] -> cost = cost + 3; goto P1

:: !visited[2] -> cost = cost + 8 ; goto P2

-> cost = cost + 2; goto end

:: else

fi;

7

end:

}

```

Fig. 2. Promela model of the sample TSP of Fig. 1

the error trace which was generated last (corresponding with this optimal min) is the optimal route.

This approach works, but is (highly) inefficient: the complete state space already contains the most optimal solution. After a single run over the state space one should be able to report on the optimal solution. The problem, however, is that we cannot compare information (e.g. the cost) obtained via different execution paths in standard SPIN. This is inherent to the application of model checkers as a black box for solving optimisation problems.

#### 3 Spin Version 4.0

SPIN version 4.0 [10] – available from [11] – supports the inclusion of embedded C code into Promela models through five new primitives:

- c\_decl: to introduce C types that can be used in the PROMELA model;

- c\_state: to add new C variables to the PROMELA model. Such new variables can have three possible scopes:

```

input: \  \, \text{Promela model} \,\, M \,\, \text{with cost added to the states.} \\ output: \  \, \text{the optimal solution min for the optimisation problem of} \,\, M.

1 \quad \min \leftarrow \text{(worst case)} \,\, \text{maximum cost} \\ 2 \quad \text{do} \\ 3 \quad \text{use Spin to check} \,\, M \vDash \Diamond(\text{cost} > \min) \\ 4 \quad \text{if (error found)} \\ 5 \quad \text{then } \min \leftarrow \text{cost} \\ 6 \quad \text{while (error found)}

```

**Fig. 3.** Algorithm to find the optimal solution for an optimisation problem using Spin

- *global* to the PROMELA model;

- local to one of the processes in the model; or

- *hidden*, which means that the variable will not end up in the state vector, but can be accessed in c\_expr or c\_code fragments.

- c\_expr: to evaluate a C expression whose return value can be used in the PROMELA model (e.g. as a guard);

- c\_code: to add arbitrary C code fragments as an atomic statement to the PROMELA model. For example, the c\_code primitive enables to include useful printf-statements in the verifier for debugging purposes.

- c\_track: to include (external) memory into the state vector.

The purpose of the new primitives is to provide support for automatic model extraction from C code. And although "it is not the intent of these extensions to be used in manually constructed models" [10], the extensions are helpful for storing and accessing global information of the verification process.

Within c\_expr of c\_code fragments one can access the global and local variables of the current state through the global C variable now of type State. The global variables of the PROMELA model are fields in a State. For example, if the PROMELA model has a global variable cost, the value of this variable in the current state can be accessed using now.cost.

As of version 4.0, the pan-verifier generated by SPIN also contains a guided simulation mode. It is no longer needed to replay error trails with SPIN.

For more details on the new features of SPIN 4.0 the reader is deferred to [10]. The rest of this paper only uses the primitives c\_state, c\_expr and c\_code.

#### 4 TSP with Branch-and-Bound

In this section, we will discuss how the new C primitives of SPIN 4.0 can be used to compute the optimal solution of a TSP more efficiently. We show how SPIN can be used to obtain the optimal solution in a single verification run. Branch-

and-Bound techniques can be used to prune the search tree. We also show how heuristics can be used to further improve the search.<sup>2</sup>

SPIN 4.0 allows us to add *hidden* c\_state variables to the pan verifier within the PROMELA model. Consequently, while exploring the state space, each time SPIN finds a better solution it can save this solution in such a *hidden* variable. To get the best route for our TSP problem with SPIN 4.0, the TSP model needs to be altered as follows:

Add a hidden, global variable best\_cost to the PROMELA model and consequently to the pan verifier. Initialise this variable best\_cost on a worst-case estimate of the cost of a schedule, e.g.,

```

c_state "int best_cost = 1000" "Hidden"

```

Due to the scope "Hidden", the variable best\_cost will *not* be stored in the state vector and will be global to all execution runs. The declaration and initialisation of best\_cost is copied verbatim to the pan.c file.

- Whenever a new solution is found (i.e. when the label end is reached), the cost for that new route is compared with the best\_cost sofar. If cost is smaller, we have found a better solution, so the variable best\_cost is updated and the trace is saved:

```

end:

c_code {

if (now.cost < best_cost) {

best_cost = now.cost;

printf("\n> best cost sofar: %d ", best_cost);

putrail();

Nr_Trails--;

}

}

```

The function putrail saves the trace to the current state (i.e. it writes the states in the current depth-first search stack to a trail-file). The statement Nr\_Trails-- makes sure that a subsequent call of putrail will overwrite a previous (less optimal) trail. Both putrail and Nr\_Trails are defined in the generated pan.c file.

Branch-and-Bound in the model. Branch-and-Bound (B&B) [3, 22] is an approach developed for solving discrete and combinatorial optimisation problems. The essence of the B&B-approach is the following:

- Enumerate all possible solutions and represent these solutions in an enumeration tree. The leaves are end-points of possible solutions and a path from the start node to a leaf represents a solution.

- While building the tree (i.e. the state space), we can stop considering descendents of an interior node, if it is certain that all paths via this node will (i) either lead to an *invalid solution* or (ii) will have *higher costs* than the best path found so far.

<sup>&</sup>lt;sup>2</sup> This paper only applies heuristics on the PROMELA level. Edelkamp et. al. [6] use a more powerful approach in HSF-SPIN, where heuristics are applied in the internals of SPIN.

The B&B-approach is not a heuristic or approximating procedure, but it is an exact, optimising procedure that finds an optimal solution.

In our PROMELA model of the TSP problem, the B&B-approach can be applied to 'prune' the state space. If in a place Pi the current cost is already higher than the best cost so far (i.e. best\_cost), it is not useful to continue searching. So at the beginning of every place Pi of our model we add the following if-statement with c\_expr expression:

```

if

:: c_expr { now.cost > best_cost } -> goto end

:: else

fi;

```

Branch-and-Bound in the property. Recall the original idea of the algorithm of Fig. 3 which iteratively checks  $\diamond$ (cost > min) to find an optimal solution. Although inefficient, due to SPIN's on-the-fly model checking algorithm, for each subsequent iteration, less of the state space will be checked. For each execution path, SPIN will stop searching as soon as it finds a state for which cost > min holds. Furthermore, SPIN will exit with an error as soon as it finds an execution path for which the final cost is lower than min. So, in a way, SPIN's on-the-fly verification algorithm already performs some B&B-functionality by default.

Using the possibilities of SPIN 4.0, we can improve the verification of the  $\diamond$ -property by replacing min with the *hidden* global variable best\_cost. We define the following macro using a c\_expr statement:

```

#define higher_cost (c_expr { now.cost >= best_cost })

```

and we check  $\Diamond$ higher\_cost. As the variable best\_cost is changed during the verification, the property that is being checked is dynamically changed during the verification!

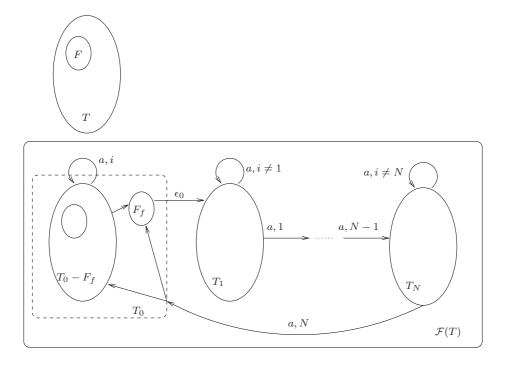

*No cycles.* Spin translates the property ⋄p to the following never-claim:

```

never { /* !<>p */

accept_init:

TO_init:

if

:: (!((p))) -> goto TO_init

fi;

}

```

Given this never-claim, the pan verifier will (i) search for states where !p does not hold (i.e. where p does hold, and thus the if-statement blocks) or (ii), due to the accept\_init-label, for each state s where !p holds, the verifier will try to find a cycle from s to itself (i.e. an acceptance cycle). For discrete optimisation problems, however, the search space will be a tree without cycles. Consequently, the search for an acceptance cycle will always be in vain and thus unneeded.

```

1 procedure dfs(s: state)

2 if error(s) then report error fi

3 add s to Statespace

4 foreach successor t of s do

5 if t not in Statespace then dfs(t) fi

6 od

7 end dfs

```

Fig. 4. Basic depth-first search algorithm [14]

It is therefore enough to let the pan verifier run in safety mode, without the -a option to check for acceptance cycles.

Note that due to Spin's *smart* double-nested depth-first search [14], this optimisation is more effective on the verification time than on the memory needed to store the state space.

Nearest Neighbour Heuristic. When using B&B-methods to solve TSPs with many cities, large amounts of computer time may be required. For this reason, heuristics, which quickly lead to a good (but not necessarily optimal) solution to a TSP, are often used. One of such heuristics is the "Nearest Neighbour Heuristic" (NN-heuristic) [22]. To apply the NN-heuristic, the salesman begins at any city and then visits the nearest city. Then the salesman goes to the unvisited city closest to the city it has most recently visited. The salesman continues in this fashion until a tour is obtained.

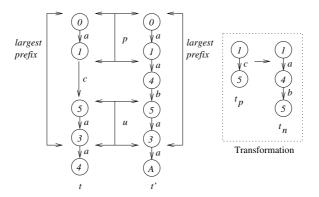

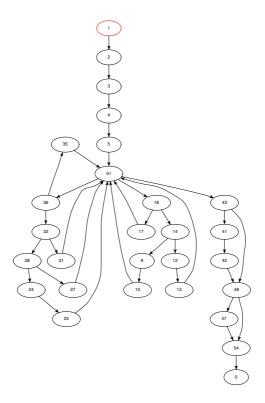

In order to apply the NN-heuristic to SPIN we must control the order in which neighbour places are selected. In order words, we must control the order of successor states in the state space exploration algorithm of SPIN. The algorithm of Fig. 4 from [14] shows a basic depth-first search algorithm which generates and examines every global state that is reachable from a given initial state. Although SPIN uses a slightly different (nested) depth-first search algorithm, for the discussion here, Fig 4 suffices.

There is only one place in the algorithm where we can influence Spin's depth-first search: line 4, where the algorithm iterates over the successor states of state s. Spin always uses the same well-defined routine to order the list of successors:

- Processes. Spin arranges the processes in reverse order of creation. That is, the process with the highest process id (pid) will be selected first.

- Statements. Within each process, SPIN considers all possible executable statements. For a statement without guards, there is at most one successor. For an if or do statement, the list of possible successors is the list of executable guards in the same order as they appear in the PROMELA model.

As the PROMELA processes can be created in any order and we are also free to order the guards within if and do clauses, we have limited control over SPIN's search algorithm from within the PROMELA model.

|                           | dim=11 | dim=12  | dim=13  | dim=14  | dim=15  |

|---------------------------|--------|---------|---------|---------|---------|

| no B&B                    | 572729 | 1878490 | 5459480 | o.m.    | o.m.    |

| unsorted, B&B in model    | 278753 | 212984  | 514332  | 2478440 | 2820880 |

| unsorted, B&B in property | 111920 | 72022   | 173309  | 1050580 | 1010080 |

| sorted, B&B in model      | 132517 | 54924   | 140075  | 1748130 | 1388100 |

| sorted BlyB in property   | 49801  | 16662   | 43240   | 737107  | 480572  |

**Table 1.** Verification results (number of states) of verifying PROMELA models of five randomly generated TSP cost matrices using different types of optimisation schemes

Fortunately, the control over the order of the guards within if-clauses is enough to apply the NN-heuristic to SPIN. To make sure that in every place Pi, SPIN will first consider the place Pj for which the cost  $c_{ij}$  is the lowest, the guards of all if-clauses are sorted on the cost  $c_{ij}$ , such that the guard with the lowest cost  $c_{ij}$  is at the top and the highest cost is at the bottom.

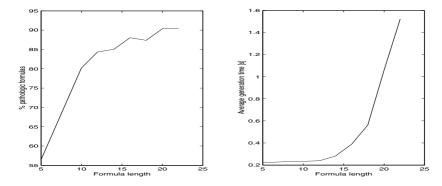

Experimental results. To compare the different approaches w.r.t. the TSP, we have carried out some experiments with some randomly generated TSPs. The original approach which lets SPIN iteratively check  $M \vDash \diamondsuit(\texttt{cost} > \texttt{min})$  has been left out of the experiments for obvious reasons. Table 1 lists the results of the experiments for randomly generated TSPs of dimension 11–15. We used a script to generate the cost-matrix for these TSPs where each  $c_{ij}$  was randomly chosen from the interval 1-100.<sup>3</sup> We used another script to generate the PROMELA models for the particular TSP as described in this section. The entry 'o.m.' stands for 'out of memory'.

From the experiments we can learn that B&B in the property is more advantageous than B&B in the model. This does not come as a suprise as due to the addition of B&B-functionality in the PROMELA model, the number of states of the TSP process increases. It is also interesting to see that the NN-heuristic really pays of. As the cost matrices are randomly generated, we cannot compare the results for the different dimensions.

#### 5 Personalisation Machine

In this section, we discuss the application of the B&B-approach to a job-shop scheduling problem. We will extend the 'Branch-and-Bound in the property' technique as discussed in Section 4 by adding more bounding conditions to the property.

Problem description. The problem itself is a simplified version of a case study proposed by Cybernetix (France) within the Advanced Methods for Timed Sys-

<sup>&</sup>lt;sup>3</sup> If the interval from which the different costs  $c_{ij}$  is (much) smaller, e.g. 1–10, the number of states drops significantly due to SPIN's state matching.

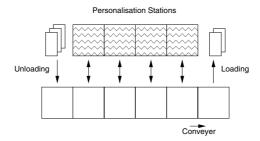

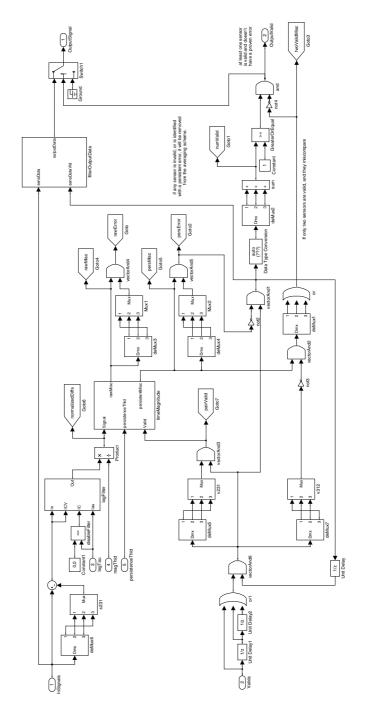

Fig. 5. Schematic overview of the personalisation machine

tems (AMETIST, IST-2001-35304) project [1]. Cybernetix is a company manufacturing machines for the personalisation of smart cards. These machines take piles of blank smart cards as raw material, program them with personalised data, print them and test them.

Fig. 5 shows a schematic overview of the personalisation machine that we discuss in this paper. Cards are transported by a *Conveyer* belt. There are NPERS *Personalisation Stations* where cards can be personalised. The conveyer is NPERS+2 positions long. The *Unloader* puts empty cards on the belt. The *Loader* removes personalised cards from the belt. The order in which the cards are loaded *from* the belt should be same as the order in which they were unloaded *onto* the belt.

The conveyer can only move a step to the right which takes tRIGHT time units. If cards are unloaded onto the belt or loaded from the belt, the conveyer cannot move. Unloading and loading can be done in parallel. Unloading and loading takes tUNLOAD resp. tLOAD time units. If after a conveyer move, an empty card is under a personalisation station, the card might be taken of the belt by the personalisation station and personalisation of the card will start immediately. The personalisation of a card takes tPERSONALISE time units. In the original case study description, tRIGHT is equal to 1, tUNLOAD and tLOAD are both 2, whereas tPERSONALISE lies between 10 and 50.

Goal. Given NPERS personalisation stations, the goal is to find an optimal schedule to personalise NCARDS cards.

PROMELA model. Modelling the personalisation machine in PROMELA is straightforward. The conveyer belt is modelled by an array of NCELLS=NPERS+2 cells. A cell is represented by a short. If a cell has the value 0 it is empty. If a cell contains a value n>0 the cell contains an unpersonalised card with number n. If n<0, the card has been personalised by one of the stations. There is one global variable time which is updated by the processes that 'consume time'. So the PROMELA model contains the following global variables:

```

short belt[NCELLS];

short time;

```

Apart from the global variables of the model, we also define a hidden c\_state variable best\_time which holds the time of the best schedule found so far. The behaviour of the model is specified by several parallel processes. The process Conveyer just moves the conveyer belt one step to the right. After updating the belt, the process increases the variable time with tRIGHT steps. The Conveyer process is modelled as follows.

The macro CARD\_ON\_BELT returns 1 if there is a card on the belt.

The other two *logical* processes that 'consume time' are the *Unloading* and *Loading* process. Because unloading and loading might happen concurrently, the behaviour of both processes is modelled by a single process UnloaderLoader. The unloading part just puts cards on the belt. The loading part will remove cards from the belt and will check that the order of the cards is still correct. If not, it sets the time to -1.

Below we only include fragments of the loading part of the UnloaderLoader process. If the last card has been taken from of the belt, we check whether the schedule found is faster than the best schedule so far. If this is the case, we update the *hidden* c\_state-variable best\_time.

```

:: atomic { (belt[LAST] == expectedCard) ->

belt[LAST] = EMPTY;

expectedCard = expectedCard-1;

= time + tLOAD;

time

if

:: expectedCard < -(NCARDS+1) -> assert(false)

:: expectedCard == -(NCARDS+1) ->

atomic {

c_code { if (now.time < best_time) {</pre>

best_time = now.time;

Nr_Trails=0;

putrail();

};

break:

}

:: else

fi

}

:: atomic { (belt[LAST] !=0 && belt[LAST] != expectedCard) ->

time = -1:

break;

```

Each personalisation station is modelled by a process PersStation(i). When an unpersonalised card n is in belt[i], a personalisation station might start personalising this card n. Unlike the other processes, the process PersStation waits for time to pass. After it has taken an card from the belt it sets its finish\_time[i] to the time that it will have finished the personalisation of n (i.e. time + tPERSONALISE). Then the process starts waiting till the time has reached finish\_time[i].

Variable time advance. Because either the conveyer or unloader might have to wait for a personalisation station to finish, we also need a process which consumes 'idle' time. In our initial, naive model we used a process Tick which just increases the time by 1 time unit. The total number of ticks was bounded by a constant. The obvious disadvantage of this method is that the process Tick can always do a time tick; even when there are no personalisation stations currently 'waiting' for the time to reach their finishing time.

Therefore, in our current model we follow Brinksma and Mader [5], who use the well-known variable time advance procedure [21]. With a variable time advance procedure, simulated time goes forward to the next moment in time at which some event triggers a state transition, and all intervening time is skipped. With respect to the personalisation machine this means that we let time jump to the finish\_time[i] > 0 which is the earliest.

Heuristics. In the discussion on the algorithm of Fig. 4 we noted that we can guide Spin's depth-first search by changing the order in which Spin considers successor states of a state s. Spin arranges the processes in *reverse* order of creation. That is, the process that is created last, will be selected first in considering the next successor state.

For optimal schedules for the 'personalisation machine' it is clear that the number of idle time steps by the TimeAdvance process should be minimized. So a step of the TimeAdvance process should be the last step to be considered by Spin. Furthermore, as personalisation takes the longest time, starting the personalisation card should be considered first by Spin.

Branch-and-Bound. Following the conclusions on the TSP, we want to apply the B&B-approach using a dynamic bound in the property. We will check \(\phi\)too\_late\_or\_wrong\_schedule, where the macro is defined as

The macro expands to a c\_expr expression which apart from the now familiar bound on the time and the test on negative time due to an incorrect schedule,

contains two additional function calls: will\_be\_too\_late and wrong\_schedule. These two functions try to decide at an early stage whether the current schedule leads to an inferior or incorrect schedule. Both C functions only use the current state (i.e. now) and the best\_time found so far.

- The function will\_be\_too\_late checks whether the minimum time to finish the cards that are still in the machine already exceeds the best\_time so far. The function only looks at the last card (i.e. the card with sequence number NCARDS) in the machine and computes the minimal time left for this card to reach the Loader.

- To signal incorrect schedules, the UnloaderLoader sets the time to -1 whenever a card is to be loaded from the belt which is out of order. It will be more advantageous, however, to discover such incorrect schedules (much) earlier. The function wrong\_schedule returns 1 if either one of the two conditions hold:

- Two personalised cards on the belt are out-of-order:  $\exists 1 \leq i, j \leq \text{NPERS} + 1 : (i < j) \land (\text{belt}[i] < 0) \land (\text{belt}[j] < 0) \land (\text{belt}[j])$

- An personalised card is under a personalisation station containing a card with a lower original sequence number:

```

\exists 1 \leq i \leq \mathtt{NPERS} : (\mathtt{belt[i]} < 0) \land (-\mathtt{belt[i]} > \mathtt{card\_in\_pers[i]}) Both functions together are coded in less than 70 lines of C code.

```

Get all optimal schedules. Due to the structure of the problem, SPIN will always find just a single (optimal) schedule for a given time. The reason for this is that for all schedules with the same end-time, in the last-but-one state, the last card will be under the Loader. Due to state matching of SPIN all these states will be regarded to be the same. To obtain all optimal schedules, an extra 'magic number' can be added to each state. The magic number ensures that each state will be unique. It is obvious that making the states unique will have a negative impact on the number of states.

Experimental results. To compare the various optimisations on the model of the 'personalisation machine', we have carried out experiments with several combinations of the B&B-optimisations discussed. For these experiments we used the following values for the time-constants: tRIGHT=1, tUNLOAD=tLOAD=2 and tPERSONALISE=10. We have verified six different versions of the model. The models can be characterised as follows:

- v1 Model which uses a naive ordering of the creation of processes: UnloaderLoader, the PersStation-processes, Conveyer and finally TimeAdvance. The B&B-functionality is isolated in the property, but we only bound on: "now.time >= best\_time || now.time < 0"

- v2 Model with an improved ordering of the processes: TimeAdvance, UnloaderLoader, Conveyer and finally the PersStation-processes. Version v2 uses the same B&B-property as v1

- v3 = v2, but adding "|| wrong\_schedule()" to the B&B property

- v4 = v2, but adding "|| will\_be\_too\_late()" to the B&B property

| Table 2. Verification results (number of states, memory consumption in Mb     |

|-------------------------------------------------------------------------------|

| and verification time in seconds) of finding the optimal schedule for PROMELA |

| models of the 'personalisation machine' using several different optimisations |

|    | NPERS= | 3 NCAR | DS=4 | NPERS=4 | )S=4  | NPERS= | 4 NCAR | DS=5 |      |

|----|--------|--------|------|---------|-------|--------|--------|------|------|

|    | states | mem    | time | states  | mem   | time   | states | mem  | time |

| v1 | 213760 | 23.2   | 1.9  | 1182600 | 122.6 | 12.3   | o.m    | o.m  | o.m  |

| v2 | 161140 | 18.4   | 1.4  | 869594  | 91.3  | 8.6    | o.m    | o.m  | o.m  |

| v3 | 125501 | 15.4   | 1.1  | 677040  | 72.1  | 6.4    | o.m    | o.m  | o.m  |

| v4 | 9709   | < 5.0  | 0.1  | 46600   | 9.0   | 0.5    | 457395 | 50.1 | 4.1  |

| v5 | 6463   | < 5.0  | 0.1  | 33000   | 7.7   | 0.3    | 304731 | 34.8 | 2.6  |

| v6 | 59715  | 9.8    | 0.5  | 477057  | 54.0  | 3.6    | o.m    | o.m  | o.m  |

```

v5 = v2, but adding "|| wrong_schedule() || will_be_too_late()" to the B&B property (so, v5 = v3 + v4)

```

Table 2 shows the results of verifying the different versions of the PROMELA model for different values of NPERS and NCARDS. It is clear that the optimisations discussed can be quite effective. The difference between the version with no optimisations at all (v1) and all optimisations enabled (v5) is nearly two orders of magnitude. Note that from Table 2 alone we cannot conclude much on the relative effectiveness of the different optimisations. Only the results between v1 and v2 and between v4 and v5 can be compared directly as apart from the different optimisations nothing has changed in the models. Looking at the results for v4 and v5, it is clear that discarding the schedules that will be too late (v5) is more effective than discarding incorrect schedules beforehand (v4). Also note that changing the creation order of the processes (v1 vs. v2) has a considerable impact on the number of states. As predicted, adding a magic number to states to obtain all optimal schedules (v6) is expensive.

#### 6 Conclusions

The use of model checkers for optimisation problems is appealing. A model checker can first be used to verify that the model of the problem is correct. Subsequently, the same model can be used to find an optimal solution for the problem. Iteratively checking  $\diamond(\texttt{cost} > \texttt{best\_so\_far})$  will eventually deliver the optimal solution, but the approach is highly inefficient. We have shown that with the new C primitives of SPIN 4.0, the optimal solution can be found in a single verification run with some minor modifications to the PROMELA model.

The search for an optimal solution can be greatly improved using B&B-techniques in the PROMELA model and/or property. A clear advantage is that the alterations can be done on the level of the PROMELA model. One does not have to alter the source code of SPIN or the verifier pan. We have seen that

v6 = v5, but adding a 'magic number' to each state (and thus obtaining all optimal schedules)

specifying the B&B-optimisations in the property has several advantages. First of all, all optimising code can nicely be isolated within the property: the PROMELA model does not have to be altered. But more importantly, specifying the B&B-behaviour in the property is more effective (w.r.t. the number of states) than adding it to the PROMELA model. Note that the LTL property that is being verified is dynamically changed during the verification.

The B&B-approach is most effective if SPIN can be guided into finding a good solution as soon as possible. Therefore it is advantageous to apply heuristics to the PROMELA model such that promising successor states are selected first in SPIN's depth-first search algorithm. On the PROMELA level, the user can reorder the guards in if- and do statements and/or can change the order of process creation (and thus the scheduling of the processes).

Earlier approaches (cite: [2, 7, 15]) have extended existing model checking algorithms with optimality criteria to guide the exploration of states. Behrmann et. al. [2], for example, annotate each state with the estimated minimum cost to reach the goal state and explore the state space by always selecting the state with the smallest minimum cost. Compared to such *local* approaches, this paper applies a more *global* approach in the sense the pruning is isolated in the property that is being checked.

The work might be extended in several ways:

- It would be interesting to see how the *global* approach with SPIN compares to the *local* approaches of [2, 15] and other, more traditional techniques for obtaining optimal solutions for optimisation problems.

- The use of model checkers to solve optimisation problems is limited to the number of states that is needed to find an (optimal) solution. For most classes of discrete optimisation problems, however, there is no need to store the complete state space as the state space is just a tree without loops. The exploration algorithm of SPIN might be changed in such a way that not all states are stored. One might turn off SPIN's state matching functionality all together, or apply a garbage collection algorithm to remove states that are not longer needed, or use a state cache.

- In this paper we used PROMELA to prune the search space of optimisation problems. SYMMSPIN [4] is a symmetry reduction package on top of standard SPIN. The idea is to prune parts of the state space for which there is no need to visit them due to the symmetric nature of the PROMELA model. A drawback of extensions of SPIN like SYMMSPIN is that they are implemented by changing the original source of SPIN or by modifying the source code of the generated pan verifier. Consequently, with each new version of SPIN, the extension might cease to work. Now that extensions can be implemented from within the PROMELA model this opens doors to packages on top of SPIN which are easier to maintain.

#### Acknowledgements

The author wishes to thank Angelika Mader for insightful discussions on the 'personalisation machine' case study. Joost-Pieter Katoen is thanked for valuable comments to improve both the contents and the presentation of the paper. Tomas Krilavičius is thanked for making available UPPAAL-models of the 'personalisation machine' and Kim G. Larsen for showing pointers to related work.

#### References

- [1] Advanced Methods for Timed Systems (AMETIST) Project. IST-2001-35304. Homepage: http://ametist.cs.utwente.nl/. 10

- [2] G. Behrmann, A. Fehnker, T. Hune, K. Larsen, P. Pettersson, and J. Romijn. Efficient Guiding Towards Cost-Optimality in UPPAAL. In T. Margaria and W. Yi, editors, Procs. of the 7th Int. Conf. on Tools and Algorithms for the Construction and Analysis of Systems (TACAS 2001), volume 2031 of LNCS, pages 174–188, Genova, Italy, April 2001. Springer. 1, 2, 15

- [3] O. S. Benli. The Branch-and-Bound Approach. In Anil Mital, editor, *Industrial Engineering Applications and Practice: Users' Encyclopedia*, 1999. CD-ROM edition, chapter available from http://http://www.csulb.edu/~obenli/. 2, 6

- [4] D. Bošnački, D. Dams, and L. Holenderski. Symmetric SPIN. In Havelund et al. [9], pages 1–19. 15

- [5] E. Brinksma and A. Mader. Verification and Optimization of a PLC Control Schedule. In Havelund et al. [9], pages 73–92. 1, 2, 3, 12

- [6] S. Edelkamp, A. L. Lafuente, and S. Leue. Directed Explicit Model Checking with HSF-SPIN. In M. B. Dwyer, editor, Model Checking Software, Procs. of the 8th Int. SPIN Workshop, volume 2057 of LNCS, pages 57–79, Toronto, Canada, May 2001. Springer. 6

- [7] A. Fehnker. Scheduling a Steel Plant with Timed Automata. In Procs. of the 6th Int. Conf. on Real-Time Computing Systems and Applications (RTCSA 1999), pages 280–286. IEEE Computer Society, 1999. 1, 15

- [8] A. Fehnker. Citius Vilius Melius Guiding and Cost-Optimality in Model Checking of Timed and Hybrid Systems. PhD thesis, University of Nijmegen, The Netherlands, April 2002.

- K. Havelund, J. Penix, and W. Visser, editors. SPIN Model Checking and Software Verification, Procs. of the 7th Int. SPIN Workshop (SPIN'2000), volume 1885 of LNCS, Stanford, California, USA, August 2000. Springer. 16, 17

- [10] G. J. Holzman. The SPIN Model Checker Primer and Reference Manual. Addison-Wesley, Boston, USA, 2003. 1, 4, 5

- [11] G. J. Holzmann. Spin homepage: http://spinroot.com/. 1, 4

- [12] G. J. Holzmann. Design and Validation of Computer Protocols. Prentice Hall, Englewood Cliffs, New Jersey, USA, 1991. 1

- [13] G. J. Holzmann. The Model Checker Spin. IEEE Transactions on Software Engineering, 23(5):279–295, May 1997.

- [14] G. J. Holzmann, D. Peled, and M. Yannakakis. On Nested Depth First Search. In J.-C. Grégoire, G. J. Holzmann, and D. A. Peled, editors, The SPIN Verification System, Procs. of the 2nd Int. SPIN Workshop (SPIN'96), volume 32 of DIMACS Series, Rutgers University, New Jersey, USA, August 1996. AMS.

- [15] K. Larsen, G. Behrmann, E. Brinksma, A. Fehnker, T. Hune, P. Pettersson, and J. Romijn. As Cheap As Possible: Efficient Cost-Optimal Reachability for Priced Timed Automata. In G. Berry, H. Comon, and A. Finkel, editors, *Procs. of the* 13th Int. Conf. on Computer Aided Verification (CAV 2001), volume 2102 of LNCS, pages 493–505, Paris, France, July 2001. Springer. 1, 2, 15

- [16] Princeton University, Mathematics Department. Traveling Salesman Problem Homepage. http://www.math.princeton.edu/tsp/.

2

- [17] G. Reinelt. The Travelling Salesman Computational Solutions for TSP Applications, volume 840 of LNCS. Springer, 1994. 2, 3

- [18] T. C. Ruys. Low-Fat Recipes for SPIN. In Havelund et al. [9], pages 287–321. 2,

- [19] T. C. Ruys. Towards Effective Model Checking. PhD thesis, University of Twente, Enschede, The Netherlands, March 2001. Available from the author's homepage.

2

- [20] T. C. Ruys and E. Brinksma. Experience with Literate Programming in the Modelling and Validation of Systems. In B. Steffen, editor, Procs. of the 4th Int. Conf. on Tools and Algorithms for the Construction and Analysis of Systems (TACAS'98), number 1384 in LNCS, pages 393–408, Lisbon, Portugal, April 1998. 1, 2, 3

- [21] G. S. Shedler. Regenerative Stochastic Simulation. Academic Press, Boston, 1993.

- [22] W. L. Winston. Operations Research Applications and Algorithms. Duxbury Press, Belmont, California, USA, third edition, 1994. 2, 6, 8

# A Requirements Patterns-Driven Approach to Specify Systems and Check Properties\*

Sascha Konrad, Laura A. Campbell, Betty H. C. Cheng\*\*, and Min Deng

Software Engineering and Network Systems Laboratory

Department of Computer Science and Engineering

Michigan State University

East Lansing, Michigan 48824 USA

{konradsa,campb222,chengb,dengmin1}@cse.msu.edu

Abstract. We previously developed a framework, Hydra, for adding formal semantics to a collection of UML diagrams that enable the automated derivation of formal language specifications for those diagrams. Recently, we have also identified a number of requirements patterns for embedded systems that includes sample UML structural and behavioral diagrams for modeling requirements and high-level design for embedded systems. This paper describes a requirements patterns-driven approach for developing UML diagrams for embedded systems, where each pattern has a constraints section to specify safety and other invariant properties. We show how the diagrams for an industrial automotive system, via specifications generated from Hydra, can be automatically analyzed for adherence to these formally specified constraints using the SPIN model checker. We developed the MINERVA framework to support the graphical construction of UML diagrams and to visualize the results from the SPIN analysis in terms of the original UML diagrams.

#### 1 Introduction

It is well-known that requirements modeling and analysis is one of the most difficult tasks in the software development process [20], but this problem is greatly exacerbated for embedded systems given the hardware constraints and the potentially complex control logic. Previously, we developed modeling/visualization and formalization frameworks and tools to facilitate the rigorous development of embedded systems. Specifically, we have tools to support the graphical modeling of requirements (MINERVA [3]), the translation of these models into formal specifications (Hydra [4, 15]) that can then be analyzed using the appropriate tools, such as the SPIN simulator and model checker [9], and the visualization of errors captured in terms of the original graphical models (MINERVA). Recently,

<sup>\*</sup> This work has been supported in part by NSF grants EIA-0000433, EIA-0130724, CDA-9700732, CC-9984726, and CC-9901017, Department of the Navy, Office of Naval Research under Grant No. N00014-01-1-0744, and in cooperation with Siemens Automotive and Detroit Diesel Corporation.

<sup>\*\*</sup> Please contact this author for all correspondences.

T. Ball and S. K. Rajamani (Eds.): SPIN 2003, LNCS 2648, pp. 18-33, 2003.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2003

we identified a number of requirements patterns for use in the development of requirements and high-level design for embedded systems [14]. We constructed a requirements pattern template, much in the spirit of the template used by Gamma et al. [7] for design patterns. This paper describes a three-pronged approach, using Hydra, MINERVA and SPIN, to facilitate the development of Unified Modeling Language (UML) diagrams for the requirements of embedded system applications that can be analyzed for the correctness of critical properties. The three components of the approach are the use of requirements patterns, the automatic generation of formal specifications, and the visualization of the analysis results of these specifications. The process is illustrated using an automotive application from industry, an air particulate filter system to reduce the amount of soot emitted from diesel truck exhaust.

Given the safety-critical nature of many embedded systems, methods for modeling and developing embedded systems and rigorously verifying behavior before committing to code are increasingly important. Currently, much of the embedded systems industry uses ad hoc development approaches [5]. The embedded systems community appears, however, to be interested in exploring how object-oriented modeling, specifically the UML [2], can be used for embedded systems [5]. Our requirements patterns use the UML to model structural and behavioral information, using class diagrams, and sequence and state diagrams, respectively. This information can be used to guide the construction of UML models for embedded systems. Our modeling tool, MINERVA, and formal specification generation tool, Hydra, enable developers to model their systems and check the models for adherence to critical properties. In addition, our visualization utilities in MINERVA depict errors detected by the analysis tools in terms of the original diagrams, thereby greatly accelerating the development and refinement process. The alternative for evaluating the UML models is to use visual inspection. A few tools that support UML diagrams enable developers to perform high-level syntactic analysis [19], or generate formal specifications, such as SDL [21], animate state diagrams and sequence diagrams [11], or generate code for simulation [8, 18]. But none of these utilities provide the collective capabilities captured by our approach and tools, nor do they attempt to reuse organized information such as that captured by our requirements patterns.

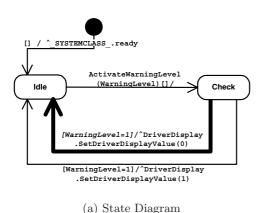

We applied the requirements patterns to several embedded systems to determine their utility. The requirements pattern template includes motivation, consequences, high-level goals, context information, constraints, and diagrams depicting templates for structure and behavior. The **Constraints** field of the template includes formal specifications of properties that should be satisfied in the context of using a given pattern [12]. The constraints are described in prose and specified in LTL (Linear Temporal Logic) according to specification patterns developed by Dwyer et al. [6]. We found that requirements patterns enable novices, guided by the structure and behavior diagrams in the templates, to quickly construct models of their systems. Also, the requirements patterns prompt developers to consider aspects of a system that might otherwise be over-

looked until much later in the development process, such as fault tolerance and safety considerations.

Requirements patterns can provide both guidance to novices of embedded systems development for determining the key elements of many embedded systems, and examples of how to model these elements with a commonly accepted diagramming notation, UML. With the formalization capability, we are able to validate (using simulation) the behavior of the requirements as captured by the state diagrams [3] within the structural context imposed by the class diagrams. Furthermore, constraints from the requirements patterns can guide novices in constructing formal properties to check against their UML models. The result is that developers can accelerate the initial development of requirements models through the use of requirements patterns, and then using our formalization work and tools, they have means to rigorously check the requirements using simulation and model checking techniques.

The remainder of this paper is organized as follows. Section 2 briefly describes our modeling/visualization and formalization frameworks and the tools instantiating them, and overviews requirements patterns. Section 3 illustrates how requirements patterns can be incorporated into our iterative modeling and analysis process for creating, analyzing, and refining UML diagrams. Section 4 contains an overview of the Diesel Filter System (a system of particulate filters to reduce soot in diesel truck exhaust) and describes the preliminary results of developing and analyzing the UML diagrams. Section 5 gives concluding remarks and discusses future investigations.

#### 2 Background

This section overviews several technologies contributing to the project, including MINERVA and Hydra that support UML, and requirements patterns that describe information typically used for describing requirements of embedded systems.

#### 2.1 Modeling/Visualization and Formalization Frameworks

We have developed a general framework [4, 15, 17] based on mappings between metamodels (class diagrams depicting abstract syntax) for formalizing a subset of UML diagrams in terms of different formal languages, including Promela and VHDL [15, 16, 17]. The formal (target) language chosen should reflect and support the intended semantics for a given domain (e.g., embedded systems). This formalization framework enables the construction of a set of rules for transforming UML models into specifications in a formal language [4]. The resulting specifications derived from UML diagrams enable either execution through simulation or analysis through model checking, using existing tools. The mapping process from UML to a target language has been automated in a tool called Hydra [15].

To complement Hydra's formalization framework for automatic generation of formal specifications, we developed a modeling and visualization framework [3]

to support a number of tasks necessary to model and analyze UML diagrams. These tasks have been automated in a tool called Minerva [3] that includes the following capabilities: graphical construction of syntactically correct UML diagrams; and visualization of consistency-checking results, simulation traces, and paths of execution that lead to errors, all in terms of UML diagrams. For this paper, we focus on the embedded systems domain, instantiating Minerva and Hydra with formalization rules for Promela to be used with the SPIN simulator and model checker [9].

#### 2.2 Requirements Patterns

In order to address the needs of requirements engineering, we developed a template to describe requirements patterns [14] by modifying the original design pattern template [7]. Modifications relevant to this paper include extending the original design pattern template with **Constraints** and **Behavior** sections that contain specification-pattern-based [6] representations of properties of interest, and sequence and state diagrams that illustrate sample behavior, respectively. Thus far, our constraints have included representations of two of Dwyer et al.'s [6] most commonly used general specification pattern categories, universality/absence (to capture invariant properties) and response (to capture cause/effect relationships in system behavior). Requirements pattern constraints provide a template for instantiating properties specific to a modeled system in terms of the UML diagrams describing the system. See [14] for further details on the requirements pattern template.

We have identified several patterns to describe requirements for the main elements of an embedded system. Figure 1 gives a list of the requirements patterns that have been identified to date with a brief description of each. The complete set of requirements patterns and their full descriptions are given elsewhere [14].

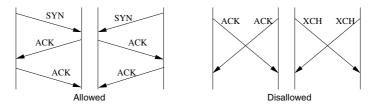

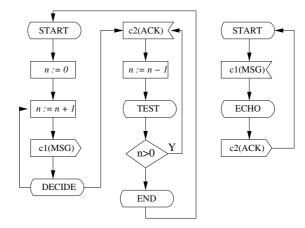

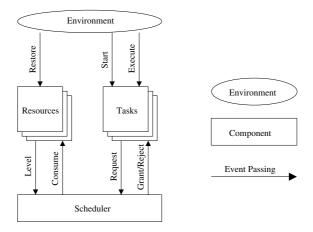

### 3 Modeling and Analysis Process

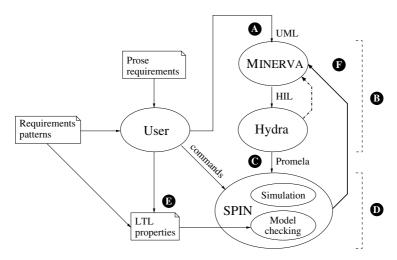

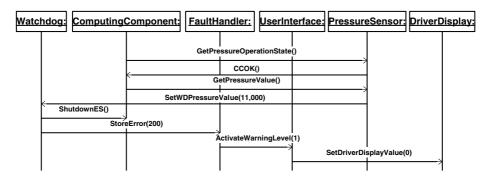

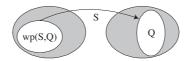

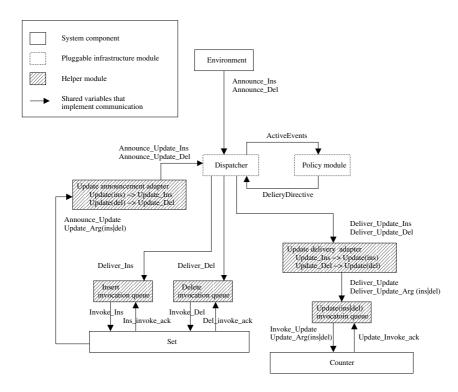

Figure 2 overviews our approach, illustrating how requirements patterns can be combined with the iterative modeling and analysis process supported by MIN-ERVA and Hydra [3, 15] (here instantiated with the model checker SPIN [9]). The user begins by selecting appropriate requirements patterns based on the requirements of the system. Using the structural and behavioral diagrams in the requirements patterns as a guide, the user constructs UML class and state diagrams in MINERVA's graphical editors (Fig. 2, part A). Hydra performs consistency checks (Fig. 2, part B), and MINERVA visualizes structural consistency-checking results (dash-dotted arc in Fig. 2, part F). (We omit discussion of these capabilities in this paper; see [3] for details.) Hydra then generates formal specifications from textual representations of UML diagrams (Fig. 2, part C); these formal specifications can be used to validate the UML diagrams through simulation using

<sup>&</sup>lt;sup>1</sup> We use Honeywell's domain model editor toolkit, DoME [10], to build the graphical editor for UML diagrams.

| Actuator-Sensor:      | How to specify various kinds of sensors and actuators and their relationships to a controller in an embedded system. |

|-----------------------|----------------------------------------------------------------------------------------------------------------------|

| Controller Decompose: | How to decompose an embedded system into different                                                                   |

|                       | components according to their responsibilities.                                                                      |

| Monitor-Actuator:     | How to increase safety and reliability by monitoring actu-                                                           |

|                       | ator behavior for errors.                                                                                            |

| Fault Handler:        | How to integrate a fault handler into an embedded system.                                                            |

| Channel:              | How to arrange communication between two components.                                                                 |

| Watchdog:             | How to monitor a device or system conditions and initiate                                                            |

|                       | corrective action(s) if a violation is found.                                                                        |

| Examiner:             | How to monitor a device and store occurring errors.                                                                  |

| User Interface:       | How to specify a user interface that is extensible and                                                               |

|                       | reusable.                                                                                                            |

| Mask:                 | How to reduce the burden placed on the computing com-                                                                |

|                       | ponent when many sensors and actuators are present,                                                                  |

|                       | whose values need to be sorted or filtered into single values                                                        |

|                       | for the computing component.                                                                                         |

| Moderator:            | How to provide an interface to support decoupling of com-                                                            |

|                       | plex subsystems.                                                                                                     |

|                       |                                                                                                                      |

Fig. 1. Current list of requirements patterns for embedded systems

SPIN (Fig. 2, part D). In addition, the user may instantiate (as LTL claims) properties from the **Constraints** section of those requirements patterns used to guide the modeling of the system (Fig. 2, part E). These LTL claims, defined in terms of attributes and states of the UML model, can then be checked against the UML diagrams (Fig. 2, part D) through model checking using SPIN. Finally, MINERVA visualizes behavior simulation and counterexample traces (solid arc, Fig. 2, part F) via state diagram animation, generation/animation of collaboration diagrams (which depict the paths of communication, or links, between objects that exchange messages), and generation of sequence diagrams, thus facilitating the debugging and refinement of the original UML diagrams.

#### 4 Modeling and Analyzing a Diesel Filter System

This section describes how we applied our modeling and analysis process to a high-level description of an automotive application obtained from one of our industrial partners, Detroit Diesel. Specifically, we depict an embedded system controlling a self-cleaning particulate filter that reduces the amount of pollutants emitted from the exhaust of diesel trucks. We illustrate how several requirements patterns interplay to guide the creation of a system model and formal constraints, and how MINERVA and Hydra enable simulation and model checking with SPIN.

Fig. 2. Overview of our approach

#### 4.1 Application Overview

An effective way to reduce particulate combustion aerosols, or soot, from diesel truck exhaust is to use particulate filters placed in a canister and inserted into the exhaust gas path. A filter comprises several tubes, with each tube consisting of ceramic fibers wound around a metallic cylindrical grid. Exhaust gas flows through the filters, out of the canister, and into the exhaust pipe. To enable the exhaust gas to flow freely through the filters, they must be cleaned periodically. Therefore, the grid wires can be electrified, causing them to heat up and burn off trapped particulates. The Diesel Filter System (DFS) is an embedded system that initiates a cleaning cycle when the differential pressure across the filter canister, as measured in *Pascals* (Pa), is within an acceptable range. The grid heating sequence will not begin if too few engine revolutions have occurred since the last time the cleaning cycle was completed, or the current engine revolutions per minute (RPMs) are too low.

#### 4.2 Requirements Patterns for the Diesel Filter System

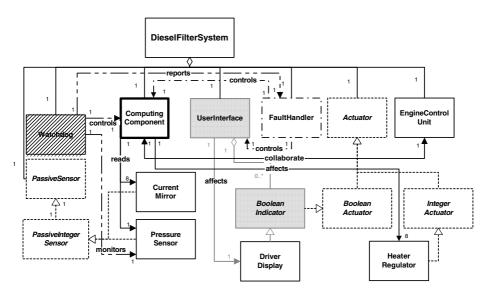

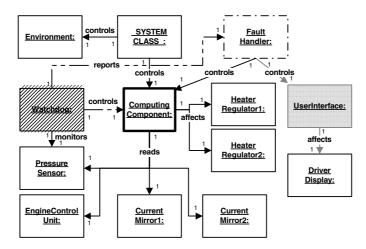

We present four requirements patterns that we identified to be appropriate for this system based on the DFS requirements [22]: Actuator-Sensor, Fault Handler, Watchdog, and User Interface Patterns. Figure 3 illustrates how the information in the **Structure** section of these patterns can be used to guide the creation of a preliminary UML class diagram for the DFS. The ComputingComponent, shown in bold in Fig. 3, plays a role in all four patterns.

Actuator-Sensor Pattern: The Actuator-Sensor Pattern, denoted by dashed boxes and lines, shows how abstract sensor and actuator classes are used to

**Fig. 3.** Requirements-pattern-guided UML class diagram of the Diesel Filter System

give a common interface to the concrete sensors (CurrentMirrors, Pressure-Sensor) and actuators (DriverDisplay, HeaterRegulators) in the DFS.

Fault Handler Pattern: The FaultHandler, illustrated with a dash-dotted box and lines, controls the ComputingComponent to initiate safety actions when errors occur. It also controls the UserInterface, warning the user that errors have occurred.

**Watchdog** Pattern: The Watchdog, denoted by a striped box and long-short-short dashed lines, monitors the PressureSensor. If it detects a violation of the maximum pressure value, then it notifies the FaultHandler of the error and initiates an emergency shutdown in the ComputingComponent.

User Interface Pattern: The User Interface Pattern is represented by the shaded boxes and lines. The UserInterface controls only one boolean indicator, the DriverDisplay, which represents a simple warning device such as an indicator light.

#### 4.3 Abstraction and Equivalence Classes

Abstraction can significantly reduce the state space needed to perform model checking; we use two techniques. First, we model only those portions of the system that are relevant to our focused analysis. In this study, we are interested in specifying and analyzing the DFS cleaning cycle. We model only those components relevant to this analysis. Additionally, we also abstract the number of heater regulators and their corresponding current mirrors from eight in the actual system down to two in our model.

Second, we determine equivalence classes for the possible values of system conditions. These equivalence classes are determined according to their impact on the behavior of the system. Generally, the operational status of a component is represented as non-working (false) or working (true), as shown in Expression (1) in Fig. 4. We model the operational status of the PressureSensor, HeaterRegulator1, and HeaterRegulator2. Ranges for other monitored values (e.g., current system pressure, number of revolutions of the engine since the last cleaning cycle, current engine speed) can be determined from the requirements, as shown in Expressions (2), (3), and (4), respectively in Fig. 4 ( $\infty$  represents the target language-dependent upper bound). We also introduce physical abstraction values for modeling purposes (Fig. 4, Expressions (5) and (6)). These values represent the interaction between components due to existing physical relationships (e.g., how much the current pressure decreases after every successful cleaning cycle in the DFS).

#### 4.4 UML Modeling for the Diesel Filter System

Based on Fig. 3 and our abstractions, we created UML object and state diagrams to model the DFS. Figure 5 overviews the UML object diagram for the DFS (attributes and methods have been elided; components attributed to the different patterns retain their shading/line characteristics from Fig. 3). The Computing-Component, the core of the system, reads values from the sensors PressureSensor, CurrentMirror1, CurrentMirror2, and the EngineControlUnit. It also sets the values of the actuators HeaterRegulator1 and HeaterRegulator2. The PressureSensor senses the current pressure. The EngineControlUnit models an interface to the engine controller to check the current engine speed (RPMs) and the total number of revolutions since the last cleaning cycle. Each CurrentMirror senses the amount of electrical current flowing through its respective HeaterRegulator. The FaultHandler processes error messages received and takes appropriate actions (defined in the FaultHandler state diagram which is not shown due to space constraints). The Watchdog monitors the PressureSensor, notifying the FaultHandler and shutting down the ComputingComponent if the pressure exceeds 10.000 Pa. The UserInterface controls the DriverDisplay, which represents a simple warning light. Additionally, our approach incorporates two special classes, an Environment class that defines the equivalence classes for system conditions of the environment as depicted in Fig. 4, and a SYSTEMCLASS\_ class that represents the aggregation of the main components of the system and non-deterministically selects values for the system and environment conditions according to the determined equivalence classes.

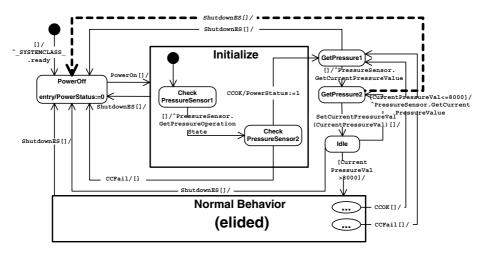

In our approach, each component has its own state diagram; however, due to space constraints, we show only the (elided) state diagram of the ComputingComponent, the central component of the DFS, in Fig. 6. The structure of this state diagram follows that of the state diagram given in the **Behavior** section of the Fault Handler pattern [14]. Specifically, it has the state PowerOff and the composite states Initialize and NormalBehavior (elided in Fig. 6). Furthermore, the three states GetPressure1, GetPressure2, and Idle represent the

$$\langle Component \rangle OperationState = \begin{cases} 0 & \text{(non-working)} \\ 1 & \text{(working)} \end{cases}$$

(1)

$$\langle Component \rangle OperationState = \begin{cases} 0 & \text{(non-working)} \\ 1 & \text{(working)} \end{cases}$$

$$CurrentSystemPressure = \begin{cases} [0; 8,000] \\ (8,000; 10,000] \\ (10,000; \infty) \end{cases}$$

$$(2)$$

Below 8,000 Pa the system remains in an idle phase; between 8,000 and 10,000 Pa the cleaning cycle starts; above 10,000 Pa the system shuts down for safety reasons.

$$TotalRPMValue = \begin{cases} [0; \ 10,000) \\ [10,000; \ \infty) \end{cases}$$

(3)

The total number of engine revolutions since the completion of the last cleaning sequence must be at least 10,000; otherwise, the cleaning sequence will not start.

$$CurrentRPMValue = \begin{cases} [0; 700) \\ [700; \infty) \end{cases}$$

(4)

The current engine speed, measured in RPMs, must be at least 700; otherwise, the cleaning sequence will not start.

$$PressureSensorCleanupValue = \begin{cases} -250\\ 300\\ 3,000 \end{cases}$$

(5)

This value determines how much the pressure decreases each time a heating element is activated. A negative value resembles a defective heating element, letting the pressure rise in every cleaning sequence.

$$HeaterCurrentConversionRatio = \begin{cases} 2\\ 3\\ 4 \end{cases}$$

(6)

This value determines the amount of increase of the current mirror value per increase of the respective heating element value. The lower the heater current conversion ratio, the faster the current value will increase on a heater value increase.

Fig. 4. Equivalence classes for system conditions

Idle phase of the DFS where the system continuously queries the PressureSensor and initiates a cleaning cycle if the pressure is found to exceed 8,000 Pa. (The dashed and bolded transitions and the italicized elements are added as later refinements based on analysis feedback; they are included in this figure due to space constraints and will be described in the next section as part of the analysis process.)

The DFS performs three main steps. First, on system activation, the DFS enters an *Initialization* phase. If the initialization is performed successfully, then the system enters an *Idle* phase. While in the *Idle* phase, the system continuously

Fig. 5. UML object diagram of the abstracted Diesel Filter System

checks the current system pressure. If a failure occurs during the initialization, then the system shuts down.

Second, if the differential pressure in the filter container exceeds 8,000 Pa, then the cleaning cycle is started. At the beginning of the cleaning cycle, the system waits for the total number of revolutions since the last cleaning cycle and the current RPMs to pass their thresholds of 10,000 and 700, respectively. In a cleaning sequence, each operational heater element is ramped up to burn off trapped particulates and ramped down afterwards. During the ramp-up process of each heater element, the system monitors the current on the corresponding

Fig. 6. UML state diagram of the ComputingComponent (elided)

current mirror to detect excess conditions and accordingly ramps down the heating element.

Third, after the completion of the cleaning cycle the DFS returns to the *Idle* phase, waiting for either the pressure to exceed 8,000 Pa again or a system shutdown message to arrive.

#### 4.5 Analysis Using Requirements and Specification Patterns